## QNIVERTER User's Guide

10067X07

APRIL 1981

ABLE COMPUTER TECHNOLOGY 1751 Langley Avenue Irvine, California 92714 (714) 979-7030 TWX 910-595-1729

#### April 1981

The material in this manual is for informational purposes and is subject to change without notice.

DEC, PDP, Unibus, and Q Bus are trademarks of Digital Equipment Corporation.

QNIVERTER is a trademark of ABLE Computer Technology.

10067x07 0380

## Contents

| SECTION | 1 | HOW        | TO USE THIS MANUAL                                             |

|---------|---|------------|----------------------------------------------------------------|

| SECTION | 2 | WHAT       | r is Qniverter                                                 |

|         |   | 2.2        | GENERAL DESCRIPTION                                            |

| SECTION | 3 | HOW        | TO INSTALL QNIVERTER                                           |

|         |   | 3.2<br>3.3 | UNPACKING QNIVERTER  VERIFY THAT YOU RECEIVED WHAT YOU ORDERED |

| SECTION | 4 | TAHW       | TO DO IF QNIVERTER DOES NOT WORK4-1                            |

|         |   | 4.2<br>4.3 | HOW TO CARE FOR QNIVERTER                                      |

| SECTION | 5 | HOW        | TO USE QNIVERTER                                               |

|         |   | 5.1        | TYPICAL PDP-11 UNIBUS SYSTEM APPLICATION                       |

| SECTION 6  | HOW   | TO PROGRAM QNIVERTER 6-1            |

|------------|-------|-------------------------------------|

| SECTION 7  | HOW   | QNIVERTER WORKS                     |

|            | 7.2   | FUNCTIONAL DESCRIPTION OF QNIVERTER |

| APPENDIX A | A Q B | BUS CONNECTORS                      |

| APPENDIX E | B UNI | IBUS CONNECTORS                     |

| APPENDIX C | SPA   | ARE PARTS LIST                      |

| APPENDIX D | ) LIS | ST OF MATERIALS D-                  |

| GLOSSARY . | o e e |                                     |

|            |       | Τ                                   |

## Figures

| 2-1<br>3-1<br>3-2<br>3-3<br>7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6<br>7-7<br>7-8<br>7-9 | QNIVERTER, MODEL 10067                       | 1 4 4 |

|-----------------------------------------------------------------------------------------|----------------------------------------------|-------|

|                                                                                         | Tables                                       | 5     |

| 7-1<br>7-2                                                                              | LOGIC BLOCKS TO BUS SIGNALS REFERENCE        | ;     |

| 7-2<br>7-3                                                                              | UNIBUS INITIATED WRITE DATA TRANSFER         | ,     |

| 7-3<br>7-4                                                                              | Q BUS INITIATED WRITE DATA TRANSER           | . (   |

| 7-5                                                                                     | Q BUS INITIATED READ DATA TRANSFER           | . 2   |

| , ,                                                                                     |                                              |       |

| 7-6                                                                                     | O RUS INTERRUPT SEQUENCE - UNIBUS ARBITRATOR | . :   |

| 7-6<br>7-7                                                                              | Q BUS INTERRUPT SEQUENCE - UNIBUS ARBITRATOR | _ (   |

| 7-6<br>7-7<br>7-8                                                                       | Q BUS INTERRUPT SEQUENCE - UNIBUS ARBITRATOR | - (   |

|  |  | ( |

|--|--|---|

|  |  | ( |

|  |  |   |

# Section 1 How to Use This Manual

Congratulations on your purchase of a QNIVERTER from ABLE COMPUTER. We are sure that it will provide you with years of satisfactory service. We have prepared this manual to help you maximize the effectiveness of the QNIVERTER in your system.

This manual is provided to assist you with the installation, use, and care of QNIVERTER; it does not provide repair information. If you have problems with your QNIVERTER, we prefer that you let us repair it in our factory.

This manual assumes that you are familiar with the PDP-11 Unibus and LSI-11 Q Bus architecture. For information about these architectures, refer to the following DEC documents:

- PDP-11 Processor Handbook

- PDP-11 Peripherals Handbook

- PDP-11 Terminals and Communications Handbook

- Microcomputer Handbook

This manual is organized into the following sections:

- Section 2 describes the QNIVERTER including its features and specifications.

- Section 3 explains how to install QNIVERTER.

- ullet Section 4 provides troubleshooting tips and tells who to call for service.

- Section 5 provides application information.

- Section 6 contains programming information.

- Section 7 describes how QNIVERTER works.

- Appendix A provides Q Bus connector assignments.

- Appendix B lists Unibus connector assignments.

- Appendix C provides a list of spare parts.

- ullet Appendix D contains the QNIVERTER list of materials.

|  |  | • |  |  |

|--|--|---|--|--|

# Section 2 What is QNIVERTER?

#### 2.1 GENERAL DESCRIPTION

The QNIVERTER is a quad-width board (see Figure 2-1) that performs one of two functions:

- Permits an LSI-11/2, LSI-11/23, or PDP-11/03 computer system to access Unibus compatible controllers and memories. The LSI-11 remains as bus arbitrator and all latency specifications are bound by the LSI-11.

- Permits a PDP-11 Unibus system to access LSI-11 compatible controllers and memories. The bus arbitration is performed by the Unibus CPU.

With QNIVERTER, memories and controllers may reside on both the Unibus and Q Bus. NPR data transfers are supported across the QNIVERTER in either direction.

The QNIVERTER installs into a quad slot of an LSI-ll backplane. A pair of Unibus connectors on the board provide connection to a Unibus cable (not supplied). The QNIVERTER's dual functions are easily user selected.

Figure 2-1: QNIVERTER, Model 10067

#### 2.2 FEATURES

QNIVERTER provides the user with a choice of applications which allow:

- Readily available Unibus devices to be used on an LSI-11 computer system, or

- Less expensive and more compact LSI-11 devices to be used on a Unibus computer system.

QNIVERTER supports the features of the LSI-11/23 including:

- Four-level interrupt structure

- Memory parity

- Full 256K byte addressing.

QNIVERTER is software transparent to the host computer.

As an added bonus, QNIVERTER provides extended bus load capabilities:

- Q Bus drive capability equivalent to an LSI-11 computer can be added to a Unibus computer system, or

- 19 Unibus loads can be added to an LSI-11 computer system.

#### 2.3 SPECIFICATIONS

#### 2.3.1 ELECTRICAL SPECIFICATIONS

Bus loading: -1 Unibus load

-1 LSI bus load

Drive Capability: -19 Unibus loads to include 50 feet of cable or less

-LSI drive capability equivalent to an LSI-ll computer

Power Required: -In a Unibus computer system--3.2 amps @ +5 volts

(which includes the Q bus terminator), ±12 volts

is not required.

-In an LSI-11 computer system--2.5 amps @ +5 volts.

#### 2.3.2 PHYSICAL SPECIFICATIONS

Size: Standard quad-width module measuring 10.45 x 8.40 inches (excluding handles).

External Connection: Two connectors compatible with a standard Unibus extender cable.

### SECTION 3

## How to Install QNIVERTER

#### 3.1 UNPACKING QNIVERTER

QNIVERTER is shipped in a special container to prevent any damage during shipment. Unpack it carefully and verify that no damage has occurred. If there is damage, notify the carrier immediately. Save the shipping carton to show proof of damage or in case the product requires shipment.

#### 3.2 VERIFY THAT YOU RECEIVED WHAT YOU ORDERED

Be sure that you have received the correct order by checking the product number on the component side of the board near the handles. The QNIVERTER product number is 10067. (See photo on page 2-1.)

If you have not received the correct equipment, notify our factory immediately.

#### 3.3 USING QNIVERTER WITH A PDP-11 SYSTEM

The QNIVERTER is shipped ready for installation in conjunction with a PDP-11 computer system. For use with an LSI-11 computer system, refer to paragraph 3.4. To be sure that QNIVERTER is ready to attach LSI-11 compatible devices to a PDP-11 Unibus, verify the following on the QNIVERTER printed circuit board:

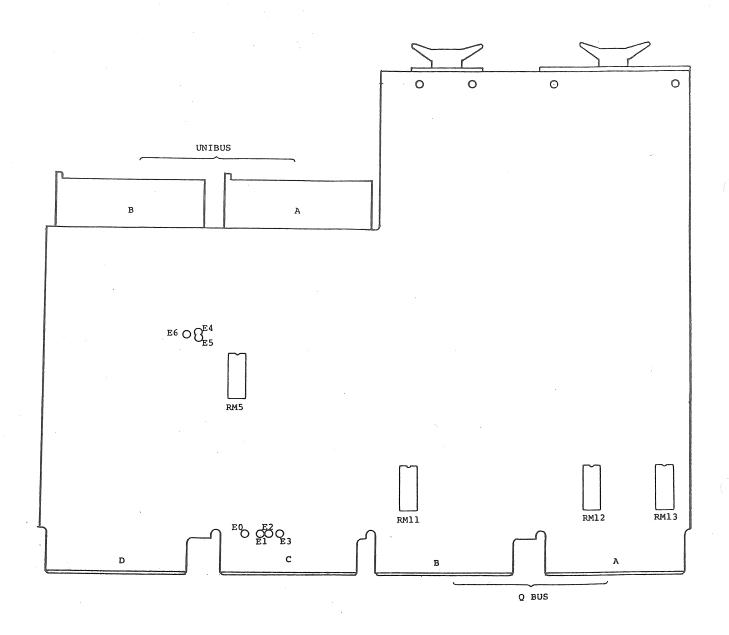

- A. E6 is jumpered to E4. (See Figure 3-1 for location of "E" points.)

- B. Resistor termination modules are installed in the following locations: (See Figure 3-1 for location of resistor modules.)

- RM11 Q Bus Termination 330 ohm pull-up, 680 ohm pull-down

- RM12 Q Bus Termination 330 ohm pull-up, 680 ohm pull-down

- RM13 Q Bus Termination 330 ohm pull-up, 680 ohm pull-down

- RM5 Unibus Termination- 390 ohm

#### 3.3.1 PDP-11 SYSTEM INSTALLATION EQUIPMENT REQUIRED

To use QNIVERTER with a Unibus computer system, the following user-supplied equipment is required:

Figure 3-1: QNIVERTER Board Layout

- Unibus cable

- Quad LSI-11 backplane for installation of QNIVERTER and LSI-11 devices

- Appropriate power sources for LSI-ll devices

#### 3.3.2 PDP-11 SYSTEM CONFIGURATION

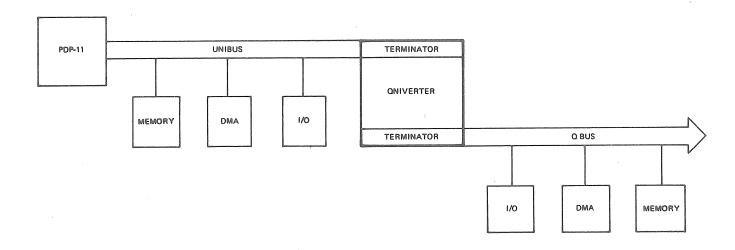

Figure 3-2 is a block diagram illustrating QNIVERTER used with a PDP-11 system. The QNIVERTER installs into the quad LSI-11 backplane slot normally occupied by the LSI-11 CPU. Guide the QNIVERTER carefully into the card guides of the selected slot. When the QNIVERTER begins to make contact with the backplane connectors, add a small amount of force to insure that the QNIVERTER is well seated in the backplane. Connection to the Unibus is accomplished by installation of one end of a Unibus cable into the connectors provided on the QNIVERTER. The other end of the Unibus cable must be installed where the Unibus terminator is installed in the present system. This places the QNIVERTER as the last device on the Unibus with the Unibus termination supplied by QNIVERTER.

Figure 3-2: Simplified Block Diagram - PDP-11 System

#### 3.4 INSTALLING QNIVERTER IN AN LSI-11 SYSTEM

The ONIVERTER is shipped configured for a Unibus arbitrator. To configure it for an LSI-ll bus arbitrator, perform the following:

- ullet Remove jumper between E6 and E4 and install a jumper between E6 and E5.

- Remove the resistor termination modules listed below from their IC sockets (store them in a safe place for possible future use):

- RM11

- RM12

- RM13

- RM5

#### 3.4.1 LSI-11 SYSTEM INSTALLATION EQUIPMENT REQUIRED

To install QNIVERTER in an LSI-11 computer system, the following user-supplied equipment is required:

- Unibus cable

- M930 Unibus terminator or equivalent

- Unibus backplane for installation of memories and controllers

- Appropriate power sources for the Unibus memories and controllers

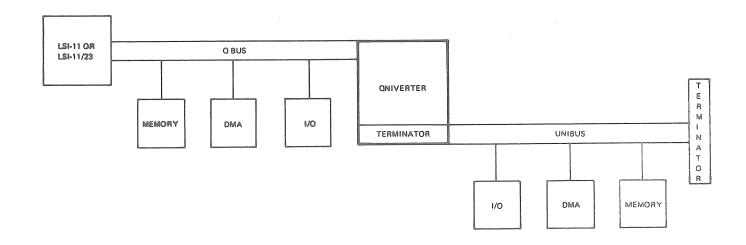

#### 3.4.2 LSI-11 SYSTEM CONFIGURATION

Figure 3-3 is a block diagram illustrating QNIVERTER installed in an LSI-11 system. The QNIVERTER is a quad-width module and requires one quad LSI-11 backplane slot for installation. Prior to installing the QNIVERTER, the LSI-11 system should be checked for proper system configuration to insure that modules are placed in the proper backplane slot. This can be used to insure that high priority devices are physically located ahead of lower priority devices. The QNIVERTER should be included in the system configuration considerations. Priority level 4 devices should be located behind the QNIVERTER; priority level 5,6, and 7 devices should be placed ahead of the QNIVERTER.

The QNIVERTER is now ready to be installed. Guide the QNIVERTER carefully into the card guides of the selected slot. When the QNIVERTER begins to make contact with the backplane connectors, add a small amount of force to insure that the QNIVERTER is well seated in the backplane.

Figure 3-3: Simplified Block Diagram - LSI-ll System

Once QNIVERTER is installed into the desired backplane slot, install a Unibus cable into the top connectors provided on QNIVERTER. The opposite end of the Unibus cable must be installed into the Unibus-In slot of a DD11 type backplane (connectors A and B) or into a Unibus-In slot of an externally mounted controller. The QNIVERTER provides Unibus termination for the beginning of the Unibus. The far end of the Unibus will require a separate terminator. Note: The Unibus controller and terminator require the appropriate power to allow system operation.

#### 3.5 INSTALLATION VERIFICATION

The QNIVERTER is totally software transparent to the arbitrating CPU system. Therefore, any diagnostic appropriate for the device attached through QNIVERTER to the arbitrating system bus may be used to verify proper installation. (Note that certain device/memory diagnostics may not be completely computer independent. Consult the diagnostic listing for the applicable devices and computer(s).)

With the QNIVERTER installed, the computer system is provided with a second bus structure: Unibus or Q bus. The arbitration of the two buses is performed by the processor in the system: either the PDP-11 or the LSI-11. The QNIVERTER is software transparent. It is important to insure that address assignments of devices on the Unibus and LSI-11 bus do not conflict. This can be accomplished by verifying that there are no duplicate address assignments.

NOTE: When installing ONIVERTER in a DEC BAll-N backplane, the jumpers between EO and E1, and between E2 and E3 must be removed.

|  |  |   | ( |

|--|--|---|---|

|  |  |   | ( |

|  |  | • |   |

|  |  |   |   |

|  |  |   |   |

|  |  |   |   |

### SECTION 4

# WHAT TO DO IF ONIVERTER DOES NOT WORK

#### 4.1 HOW TO CARE FOR QNIVERTER

ABLE products are designed to provide years of service with a minimum of care. Here are a few tips to help you avoid problems.

- If a printed circuit board is frequently inserted and removed, it tends to build up a gum-like residue on the contacts. Clean this residue off using alcohol or freon or by gently rubbing with a pencil eraser. (Rubbing vigorously can remove some of the gold on the contacts, so go easy.)

- Every six months remove each printed circuit board and clean off any accumulated dust. Dust can impede air flow. While the board is out, inspect it for any visual evidence of a potential problem such as damaged components, loose connections, etc.

- Schematics for your QNIVERTER can be ordered from the ABLE factory. Order document number 10067003.

- If you wish to maintain a spare parts inventory, refer to the recommended list in Appendix C.

- If a problem arises with the operation of your QNIVERTER, follow the steps outlined in the following sections.

#### 4.2 TROUBLESHOOTING TIPS

If QNIVERTER does not function properly, verify proper installation of the board as follows:

- Using Sections 3.3 and 3.4 verify that the jumper selection and resistor module installation are correct.

- Verify that QNIVERTER is properly installed into an LSI backplane. Refer to appropriate DEC literature for backplane information.

- Verify that the Unibus cable is installed correctly with notches aligned and is firmly seated in the QNIVERTER Unibus connectors.

- 4. Check the +5 volts power on the LSI backplane and Unibus backplane. Use a voltmeter and measure from ground to +5 volts on pin CA2, DA2, AA2, or BA2 on the backplane. Power should be +5.0 volts ±5%. If the power is not within this range, adjust the power supply.

5. Check that there are no vacant slots (missing bus grants) between ONIVERTER and other modules in the backplane.

If QNIVERTER still does not function properly, call ABLE as described in the following sections.

#### 4.3 WHO TO CALL FOR SERVICE WITHIN THE UNITED STATES

ABLE's goal is to provide each customer with a product that works well in his system. We design and build our products to provide high reliability and to minimize problems. When a problem does arise, it is our intent to do everything in our power to quickly and efficiently solve it.

If your QNIVERTER does not function properly and you are within the United States, contact our Product Support Center before sending it for repair:

ABLE COMPUTER 1751 Langley Avenue Irvine, California 92714

> (714) 979-7030 TWX 910-595-1729

If your product requires repair, we prefer that you return it to the factory. Use the original container from your QNIVERTER or a corregated cardboard carton with at least one inch of cushioning material on all sides. Ship it to the above address. Include a description of the problem and a hard copy of the failure mode or diagnostic printout when available. Be sure to include your name, address, and telephone number:

Refer to the warranty and service documents shipped with QNIVERTER or call our Product Support Center for further information.

#### 4.4 WHO TO CALL FOR SERVICE OUTSIDE THE UNITED STATES

ABLE's goal is to provide each customer with a product that works well in his system. We design and build our products to provide high reliability and to minimize problems. When a problem does arise, it is our intent to do everything in our power to quickly and efficiently solve it.

If your QNIVERTER does not function properly, contact your local distributor or telex ABLE COMPUTER for the name and address of your local distributor:

TWX 910-595-1729

## SECTION 5

### How to Use QNIVERTER

#### 5.1 TYPICAL PDP-11 UNIBUS SYSTEM APPLICATION

This application allows the user of PDP-11 Unibus systems to take advantage of the often lower-cost peripherals (and memories) available for the LSI-11 computer. Figure 3-1 is a block diagram of a typical application. The QNIVERTER and LSI-11 peripheral devices or memories are installed in an LSI-11 quad backplane and supplied with +5 volt power. The QNIVERTER is installed in the backplane slot normally occupied by the LSI-11 processor. The QNIVERTER, other devices, and memories in the LSI-11 backplane are connected to a PDP-11 Unibus computer system by a standard Unibus extender cable connected between the top side of the QNIVERTER and the last Unibus slot (A & B) in the PDP-11 backplane. Appendix B contains a Unibus connector list. The QNIVERTER is electrically the last device on the Unibus and provides the far-end Unibus termination.

QNIVERTER provides the system with a second bus structure, the LSI-ll Q bus. The arbitration of the two buses is performed by the PDP-ll processor located on the Unibus.

#### 5.2 TYPICAL LSI-11 Q BUS APPLICATION

This application allows the wider range of PDP-11 Unibus peripherals and memories to be used with the LSI-11 computer. Figure 3-2 is a block diagram of a typical application. The QNIVERTER can be installed in any quad slot of the LSI-11, LSI-11/2, LSI-11/23, or PDP-11/03 systems. Other LSI-11 interfaces and memories can be located either ahead or behind the QNIVERTER. Devices located behind the QNIVERTER have a lower priority (both interrupt and NPR/DMA) than the Unibus devices attached to the QNIVERTER.

The Unibus peripherals and memories are installed in a Unibus backplane which must be supplied with the appropriate power. An M930 terminator (or equivalent) must be the last device installed in the Unibus backplane. The Unibus backplane is connected to the QNIVERTER with a standard Unibus extender cable connected between the first Unibus connectors in the Unibus backplane and the connectors on the top end of the QNIVERTER. Appendix A contains a Q bus connector list; Appendix B contains a PDP-11 Unibus connector list.

The QNIVERTER provides the LSI-ll system with a second bus structure, Unibus. The LSI-ll processor controls the arbitration of both buses.

# Section 6 How to Program QNIVERTER

QNIVERTER provides the system of which it is a part with a second bus structure: Unibus or Q bus. The QNIVERTER is completely software transparent to the host (arbitrating) computer. Note that QNIVERTER is designed to operate with a single computer performing bus arbitration; it is not intended to be used as an interprocessor coupler.

Since QNIVERTER is software transparent to the host computer, any diagnostic appropriate for the device(s) being connected through QNIVERTER to the system may be used to verify system operation. Note that certain device/memory diagnostics may not be completely computer independent. Consult the diagnostic listing for the applicable devices and computer(s).

NOTE: THE MOST IMPORTANT CONSIDERATION IS TO INSURE THAT ADDRESS ASSIGNMENTS OF DEVICES ON THE UNIBUS AND Q BUS DO NOT CONFLICT.

# Section 7 How QNIVERTER Works

This section describes how QNIVERTER works. The first subsection describes the major functional elements of QNIVERTER. The second subsection lists and describes the Unibus I/O signals. The third subsection lists and describes the Q bus I/O signals. The first subsection descriptions are referenced to a block diagram, Figure 7-1, that illustrates the relationship among the functional units of QNIVERTER, and timing diagrams supplemented by descriptive tables that illustrate the relationship among the signals of the buses.

#### 7.1 FUNCTIONAL DESCRIPTION OF QNIVERTER

The QNIVERTER matches the characteristics of the Unibus and Q bus. It does this "characteristic matching" bidirectionally; Q bus compatible devices can be connected into a PDP-11 (Unibus) computer system, and Unibus compatible devices can be connected into an LSI-11 (Q Bus) computer system. Note that the QNIVERTER cannot be used as an inter-computer coupler. Only one processor is the system arbitrator. The user positions a jumper in QNIVERTER to select either the Unibus or the Q bus as the source of the system arbitration.

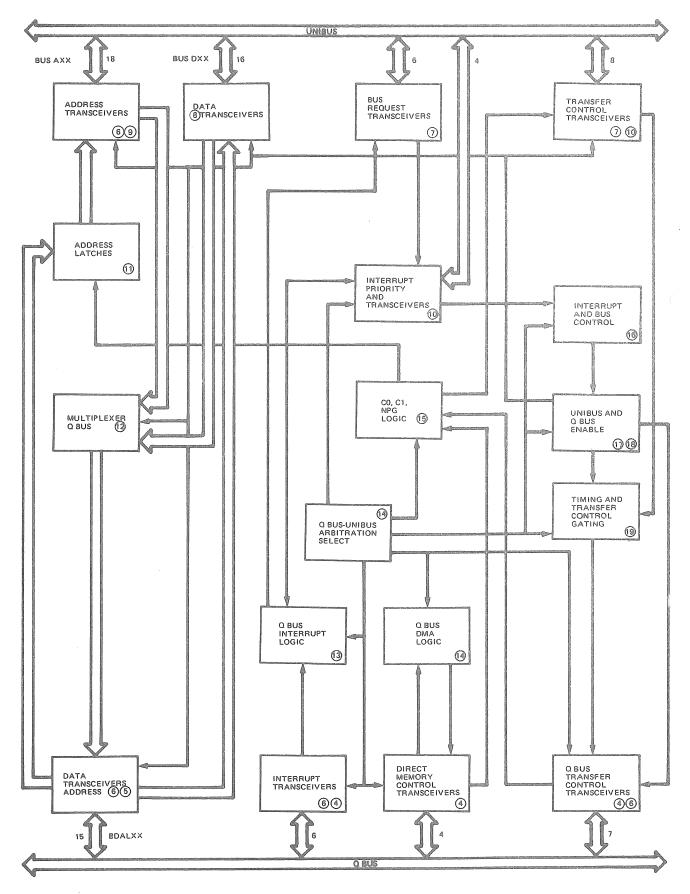

Figure 7-1 is a block diagram of the QNIVERTER. The blocks can be grouped into four major categories. The blocks within a category perform related functions.

The major categories are as follows:

- Bidirectional information transfer

- Bidirectional bus request and interrupt priority transfer

- Bidirectional information transfer control and direct-to-memory transfer control

- QNIVERTER timing and control

Table 7-1 lists the logic blocks in each category and relates the Unibus/Q bus signals to the logic blocks (when applicable).

Figure 7-1: Block Diagram QNIVERTER

| CAT | EGORY_                                                     | LOGIC BLOCKS                                                                                                                                                        | Q BUS/UNIBUS SIGNALS                                                            |

|-----|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Α.  | Information<br>Transfer                                    | 1. Unibus Address Transceivers 2. Unibus Data Transceivers 3. Q Bus Multiplexer                                                                                     | BUS-A00 to BUS-A17 BUS-D00 to BUS-D15 BUS-A00 to BUS-A17 and BUS-D00 to BUS-D15 |

| В.  | Bus Request and                                            | <ol> <li>Q Bus Data/Address Transceivers</li> <li>Q Bus Address Latches</li> </ol>                                                                                  | BDAL00 to DBAL17<br>Q Bus Address Lines                                         |

| υ.  | Interrupt Priority                                         | <ol> <li>Bus Request Transceivers</li> <li>Interrupt Priority and Bus<br/>Grant Transceivers</li> </ol>                                                             | BUS-BR4 to BUS-BR7,<br>BUS-INTR, BUS-SACK<br>BUS-BG4 to BUS-BG7                 |

|     |                                                            | 3. Q Bus Interrupt Logic 4. Q Bus Interrupt Transceivers                                                                                                            | BIRQ4 to BIRQ7,<br>BIAKI, BIAKO                                                 |

| C.  | Information Transfer Control and Direct-to- Memory control | 1. Transfer Control Transceivers                                                                                                                                    | BUS-MSYN, BUS-SSYN BUS-CO, BUS-C1, BUS-BBSY, BUS-INIT, BUS-PB, BUS-NPR, BUS-NPG |

|     |                                                            | <ol> <li>CO, Cl, and NPG Logic</li> <li>Q Bus DMA Logic</li> </ol>                                                                                                  |                                                                                 |

|     |                                                            | <ul><li>4. Direct Memory Control Transceivers</li><li>5. Q Bus Transfer Control Transceivers</li></ul>                                                              | BDMR, BSACK, BDMGI, BDMGO BSYNC, BDIN, BDOUT, BINIT, BWTBT, BRPLY, BBS7         |

| D.  | QNIVERTER Timing and Control                               | <ol> <li>Q Bus-Unibus Arbitration Select</li> <li>Unibus and Q Bus Enable</li> <li>Interrupt and Bus Control</li> <li>Timing and Transfer Control Gating</li> </ol> |                                                                                 |

Table 7-1: Logic Blocks to Bus Signals Reference

Since the PDP-11 Unibus and the LSI-11 Q bus were developed by the same manufacturer, signal transfer concepts, data word widths, and address word widths are similar. The differences between the two bus structures occurred because the LSI-11 processor is microprocessor-chip based. Pinout restrictions on the microprocessor chip dictated that the number of bus lines be reduced from the 56 lines available on the Unibus to some number within the physical capability of a standard 40-pin integrated circuit package. The number of control and information lines on the Q bus is 35. The largest reduction of lines was realized by time sharing the 16 data lines with the 18 address lines on the Q bus, a reduction of 16 lines over the Unibus (the Unibus has separate data and address lines). Other reductions were made by changing slightly the concept of granting "bus mastership" on different priority levels.

In the Unibus system the arbitration section of the processor received requests for the use of the Unibus over four priority-structured bus request lines. The arbitrator responded to bus requests over four bus grant lines. The LSI-11 and LSI-11/2 implemented only one bus request and one bus grant, permitting only one level of interrupt priority. The LSI-11/23 permits 4 level interrupt priority as well as allowing addressing up to 128K words.

In addition to the preceding bus-concept differences, there are timing differences between the two buses. The LSI-11, Q Bus, processor is micro-processor-chip based and is therefore slower than the MSI/SSI based processor on the Unibus.

Therefore, the primary tasks required of the QNIVERTER are:

- Multiplex addresses and data from the Unibus onto the single 18-bit address/data lines of the Q bus and demultiplex the Q bus address/data lines onto the separate address and data lines of the Unibus.

- Bidirectionally match the grant/request signals with the Q bus interrupt signals

- Bidirectionally match the NPR and DMA requests

- Bidirectionally match the timing among the signals of the two buses.

As mentioned previously only one processor can be in the system of which the QNIVERTER is a part. A jumper in the QNIVERTER Q Bus-Unibus Arbitration Select logic is positioned so that the logic of the QNIVERTER responds properly to the controlling computer. This jumper establishes either the Unibus as arbitrator or the Q bus as arbitrator. The controlling computer is attached to the arbitrating bus.

Throughout the following discussion, the function of the individual logic elements is only briefly described; in most cases the name of the logic block describes the function of the block, i.e., transceiver (buffers and conducts signals in both directions), latch (storage element), etc.. This material is more concerned with the relationship among the logic elements while transferring information or control between the two buses. Thus, the descriptive material is referenced to timing diagrams that show the relationship among the bus signals when either the Unibus or the Q bus is arbitrator.

#### 7.1.1 QNIVERTER TIMING AND CONTROL

As listed in Table 7-1 the logic blocks that make up the QNIVERTER timing and control section are as follows:

- O Bus-Unibus Arbitration Select

- Unibus and Q Bus Enable

- Interrupt and Bus Control

Timing and Transfer Control Gating .

When the QNIVERTER is installed in a system, the user positions a jumper in the Q Bus-Unibus Arbitration Select logic to match the characteristics of the QNIVERTER with the controlling processor, which will be positioned either on the Unibus or the Q bus. The two signals generated by this logic (UARBT and QARBT) effect every element of QNIVERTER and set the rest of the control logic into the proper mode of operation.

The Unibus and Q Bus Enable logic comprises a group of gates, a flip-flop, and a multiplexer controlled by the Q Bus-Unibus Arbitration Select logic. The gates develop outputs for the multiplexer based upon the arbitrator and the requested type of transfer (Unibus to Q bus, Q bus to Unibus). The multiplexer gates enable signals to the information transfer section of the QNIVERTER. This logic "steers" data between the two buses properly regardless of the arbitrator. It:

- A. Controls the Q bus multiplexer

- B. Clocks the address latches

- C. Enables the Q bus data drivers

- D. Enables the Unibus data and address drivers.

The Interrupt and Bus Control logic is the interface between the bus requests from the Unibus and the interrupt circuit of the Q bus when the Q bus is arbitrator. Note that bus requests from Unibus devices are translated by the QNIVERTER into interrupt requests to the LSI-ll when the Q bus is arbitrator.

The Timing and Transfer Control Logic match the characteristics of the following signals:

| UNIBUS | Q BUS            |

|--------|------------------|

| MSYN   | SYNC             |

| SSYN   | BDOUT, BDIN      |

|        | $\mathtt{BRPLY}$ |

This logic also contains the Q bus parity error detect gates.

#### 7.1.2 INFORMATION TRANSFER

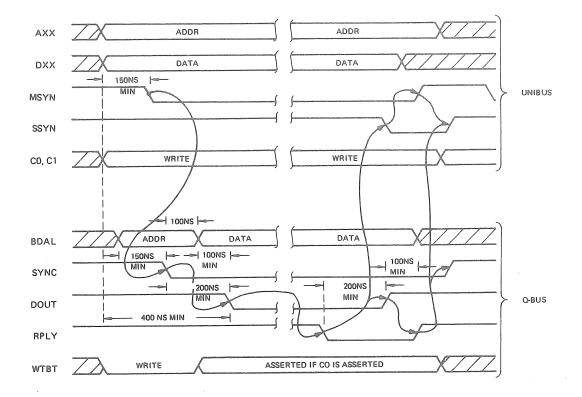

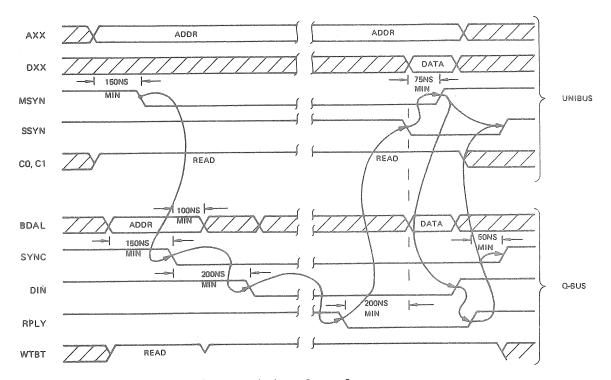

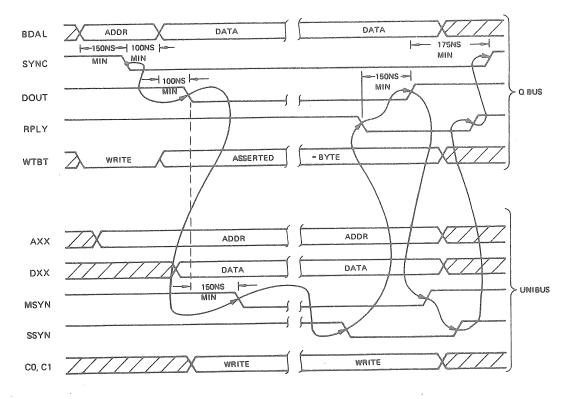

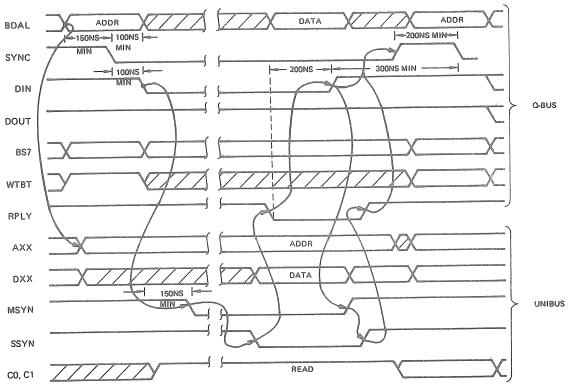

This section of logic transfers addresses and data between the Unibus and the Q bus. Either write or read data transfers can be initiated by either the Unibus or the Q bus, regardless of which bus is the arbitrator. Figure 7-2 and Table 7-2 illustrate the relationship among the Unibus and Q bus data transfer signals, addresses, and data lines during a Unibus-initiated write sequence. Figures and Tables 7-3, 7-4, and 7-5 illustrate the following transfer sequences:

7-3 Unibus-initiated read

7-4 Q bus-initiated write

7-5 Q bus-initiated read

During the transfer sequences the Q bus multiplexer, address latches, and driver sections of the bus transceivers are controlled by signals from the Unibus and Q bus Enable logic. The transfer control signals from the two buses are conditioned by the Timing and Transfer Control Gating logic. The signal source for controlling the Q bus multiplexer and address latches is the conditioned Q bus SYNC signal.

Figure 7-2: Unibus Initiated Write

| STEP                            | UNIBUS                                                                                                                               | QNIVERTER                                                                                                                                                                        | Q BUS                                               |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 1.                              | a. Device address on bus. b. Data on bus. c. Cl asserted. C0 asserted if byte transfer, negated if word transfer. d. MSYNC asserted. |                                                                                                                                                                                  |                                                     |

| 2.                              |                                                                                                                                      | a. Gate address to BDAL lines. b. Assert WTBT. If CO asserted WTBT remains asserted through cycle. If CO negated, negate WTBT within 100 ns after SYNC asserted. c. Assert SYNC. |                                                     |

| 3.                              |                                                                                                                                      | <ul><li>a. 100 ns after SYNC asserted replace address with data on BDAL lines.</li><li>b. 200 ns after SYNC asserted, assert DOUT.</li></ul>                                     |                                                     |

| 4.                              |                                                                                                                                      |                                                                                                                                                                                  | When data received by addressed device assert RPLY. |

| 5.                              |                                                                                                                                      | <ul><li>a. After 200 ns generate<br/>SSYN.</li><li>b. Negate DOUT.</li><li>c. After 100 ns remove data<br/>from BDAL.</li></ul>                                                  |                                                     |

| <ul><li>6.</li><li>7.</li></ul> | Negate MSYN.                                                                                                                         | a. Negate SSYN.                                                                                                                                                                  | Negate RPLY                                         |

| 8.                              | TRANSFER SEQUENCE COMP                                                                                                               | b. Negate WTBT if CO has been asserted.                                                                                                                                          |                                                     |

Table 7-2: Unibus Initiated Write Data Transfer

Figure 7-3: Unibus Initiated Read

Figure 7-4: Q Bus Initiated Write

| STE | P UNIBUS                           | QNIVERTER                                       | Q BUS                                                       |

|-----|------------------------------------|-------------------------------------------------|-------------------------------------------------------------|

| 1.  | a. Device address<br>on bus.       |                                                 |                                                             |

|     | b. CO, Cl negated.                 |                                                 |                                                             |

|     | c. MSYNC asserted.                 |                                                 |                                                             |

| 2.  |                                    | a. Gate address to<br>BDAL lines.               |                                                             |

|     |                                    | b. Assert SYNC.                                 |                                                             |

|     |                                    | c. Delay 200 ns,<br>assert DIN.                 | · ·                                                         |

| 3.  |                                    |                                                 | Addressed device. Assert RPLY and place data on BDAL lines. |

| 4.  |                                    | a. Gate data from BDAL<br>to Unibus data lines. | · .                                                         |

|     |                                    | b. Assert SSYN.                                 |                                                             |

| 5.  | a. Input data and<br>negate MSYNC. |                                                 |                                                             |

| 6.  |                                    | Negate DIN                                      |                                                             |

| 7.  |                                    |                                                 | Negate RPLY and remove data on BDAL lines                   |

| 8.  |                                    | Negate SSYN                                     |                                                             |

| 9.  | TRANSFER SEQUENCE COI              | MPLETED                                         |                                                             |

Table 7-3: Unibus Initiated Read Data Transfer

| STEP | Q BUS                                             | QNIVERTER                                                           | UNIBUS                                                 |

|------|---------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|

| 1.   | a. Address on<br>BDAL lines.                      |                                                                     |                                                        |

|      | b. Assert WTBT.                                   |                                                                     | ·                                                      |

|      | c. 150 ns later<br>assert WTBT.                   |                                                                     |                                                        |

| 2.   |                                                   | a. Gate Address from<br>BDAL to Unibus AXX<br>lines.                |                                                        |

|      | ·                                                 | <ul><li>b. Assert Cl. Assert</li><li>CO if byte transfer.</li></ul> |                                                        |

| 3.   | a. Negate WTBT if<br>word transfer.               |                                                                     |                                                        |

|      | b. Replace address<br>with data on<br>BDAL lines. |                                                                     |                                                        |

|      | c. Assert DOUT.                                   |                                                                     |                                                        |

| 4.   |                                                   | a. Gate data from BDAL<br>to Unibus DXX Lines.                      |                                                        |

|      |                                                   | b. Assert MSYN.                                                     |                                                        |

| 5.   |                                                   |                                                                     | When addressed device<br>accepts data, assert<br>SSYN: |

| 6.   |                                                   | Assert RPLY.                                                        |                                                        |

| 7.   | Negate DOUT and<br>remove data on<br>BDAL lines.  |                                                                     |                                                        |

|      | BDAL TIMES.                                       |                                                                     |                                                        |

| 8.   |                                                   | Negate MSYN                                                         |                                                        |

| 9.   |                                                   |                                                                     | Negate SSYN                                            |

| 10.  |                                                   | Negate RPLY.                                                        |                                                        |

| 11.  | Negate SYNC                                       |                                                                     |                                                        |

|      | TRANSFER SEQUENCE CO                              | OMPLETE                                                             | '                                                      |

Table 7-4: Q BUS Initiated Write Data Transfer

Figure 7-5: Q-Bus Initiated Read

As listed in Table 7-1 the logic blocks that make up the QNIVERTER information transfer section are as follows:

- Unibus Address Transceivers

- Unibus Data Transceivers

- Q Bus Multiplexer

- Q Bus Data/Address Transceivers

- Q Bus Address Latches

An important feature of the QNIVERTER is the bus termination characteristics when used with either a Unibus-arbitrated system or a Q bus-arbitrated system. Terminating resistor modules are permanently installed on all Unibus input/output lines. Removable terminating resistor modules are installed on the Q bus input/output lines when the QNIVERTER is used in a Unibus-arbitrated system. These resistor modules are removed, however, when QNIVERTER is used in a Q bus-arbitrated system because line termination is provided by the LSI-ll computer.

| STEP | Q BUS                                          | QNIVERTER                               | UNIBUS                                              |

|------|------------------------------------------------|-----------------------------------------|-----------------------------------------------------|

| 1.   | a. Address on BDAL<br>lines.                   |                                         |                                                     |

|      | b. 150 ns later<br>assert SYNC.                |                                         |                                                     |

| 2.   |                                                | a. Gate address from BDAL to AXX lines. |                                                     |

|      |                                                | b. Negate CO and Cl.                    |                                                     |

| 3.   | Assert DIN.                                    |                                         |                                                     |

| 4.   |                                                | Assert MSYN                             |                                                     |

| 5.   |                                                |                                         | a. Addressed device<br>asserts SSYN.                |

|      |                                                |                                         | b. Addressed device<br>places data on<br>DXX lines. |

| 6.   |                                                | a. Assert RPLY                          |                                                     |

|      |                                                | b. Gate data from DXX to BDAL lines.    |                                                     |

| 7.   | Input data on<br>BDAL lines and<br>negate DIN. |                                         |                                                     |

| 8.   |                                                | a. Negate MSYN                          |                                                     |

|      |                                                | b. Negate RPLY                          |                                                     |

| 9.   | Negate SYNC                                    |                                         |                                                     |

| 10.  |                                                |                                         | Negate SSYN and remove data on DXX lines.           |

|      | TRANSFER SEQUENCE COMPLETED                    |                                         |                                                     |

Table 7-5: Q BUS Initiated Read Data Transfer

#### 7.1.3 BUS REQUEST AND INTERRUPT PRIORITY

As listed in Table 7-1 the logic blocks that make up the QNIVERTER bus request and interrupt priority section are as follows:

- Bus Request Transceivers

- Interrupt Priority and Bus Grant Transceivers

- Q Bus Interrupt Logic

- Q Bus Interrupt Transceivers

The state of this logic, the order in which signals are transferred, depends upon which bus is the arbitrator. The order of signal flow is established by the Q bus-Unibus arbitration select logic.

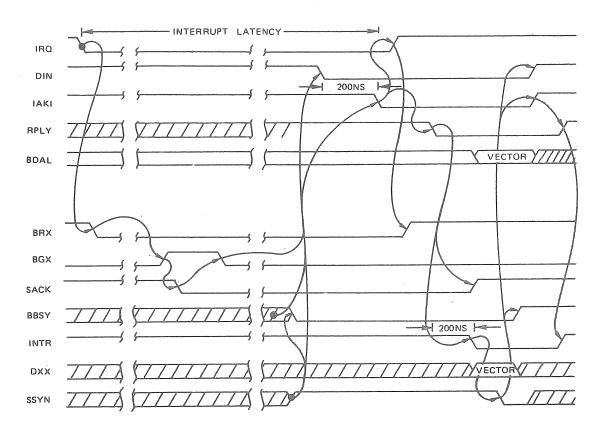

Figure and Table 7-6 illustrate the signal sequence for an interrupt request when the Unibus is arbitrator. When the Unibus is arbitrator, the bus request and interrupt driver sections of the Unibus transceivers are enabled and the interrupt drivers in the Q bus transceivers are disabled. Note that the receiver sections of all transceivers are always enabled.

As mentioned in paragraph 7.1, one of the major differences between the Unibus and the Q bus is in the interrupt logic of the buses. Interrupts on the Unibus must first request use of the bus, receive a bus grant (on one of four levels), then generate an interrupt accompanied by the device address (vector). On the Q bus the use of the bus is assumed and interrupts are requested on one of four levels, which establishes priority among the devices on the Q bus.

Note from Figure 7-6 that a Q bus IRQ on one of four levels is gated onto one of the four BR lines of the Unibus. The BG signal from the Unibus is compared with the Q bus IRQ signals in the Q bus interrupt logic to generate the DIN signal and establish IAKI and RPLY conditions to the interrupting device on the Q bus. This device then places its address on the BDAL lines and the conditioning circuits in the QNIVERTER generate Unibus signal SACK, BBSY, INTR, place the Q bus data (vector) on the Unibus data drivers, and waits for the processor to accept the vector by generating a SSYN.

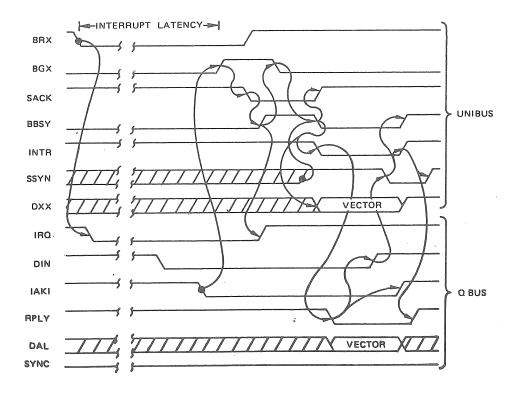

Figure and Table 7-7 illustrate the signal sequence for an interrupt request when the Q bus is arbitrator. Bus requests (BRX) are connected to IRQ lines by the driver section of the interrupt transceivers. The IAKI signal from the Q bus enables a group of gates in the interrupt priority and transceivers logic that connect the outputs of a priority register to the Unibus BG line associated with the requesting device. The requesting device then generates the SACK, BBSY, and INTR signals (most of which are ignored by the Q bus), and places its vector address on the Q bus via the Q bus multiplexer and Q bus address/data drivers.

Figure 7-6: Interrupt Sequence - Unibus Arbitrator

Figure 7-7: Interrupt Sequence - O Bus Arbitrator

| STEP | Q BUS                                                                  | QNIVERTER                                                 | UNIBUS        |

|------|------------------------------------------------------------------------|-----------------------------------------------------------|---------------|

| 1.   | IRQ asserted                                                           |                                                           |               |

| 2.   |                                                                        | BRX asserted                                              |               |

| 3.   |                                                                        |                                                           | BGX asserted. |

| 4.   |                                                                        | Unibus SACK asserted                                      |               |

| 5.   |                                                                        |                                                           | Remove BGX    |

| 6.   |                                                                        |                                                           | Remove BBSY   |

| 7.   |                                                                        | a. Assert DIN                                             |               |

|      |                                                                        | b. 150 ns later<br>assert IAKl                            |               |

| 8,   | Negate IRQ                                                             |                                                           |               |

| 9.   |                                                                        | Remove BRX                                                |               |

| 10.  | Interrupt device<br>places vector on<br>BDAL lines and<br>asserts RPLY |                                                           |               |

| 11.  |                                                                        | Gate Interrupt<br>Vector from BDAL<br>lines to DXX lines. |               |

| 12.  |                                                                        | a. Assert INTR                                            |               |

|      |                                                                        | b. 1                                                      |               |

| 13.  |                                                                        | a. Negate DIN                                             |               |

|      |                                                                        | b. Negate IAKl                                            |               |

| 14.  | Negate RPLY                                                            |                                                           |               |

| 15.  |                                                                        | a. Negate BBSY b. Remove vector from                      |               |

|      |                                                                        | DXX lines.                                                |               |

|      |                                                                        | c. Negate INTR                                            |               |

| 16.  |                                                                        |                                                           | Negate SSYN   |

|      | SEQUENCE COMPLETED                                                     |                                                           | 1             |

Table 7-6: Q BUS Interrupt Sequence-Unibus Arbitrator

| STEP | UNIBUS                          | QNIVERTER                                    | Q BUS                                               |

|------|---------------------------------|----------------------------------------------|-----------------------------------------------------|

| 1.   | Assert BRX                      |                                              |                                                     |

| 2.   |                                 | Assert IRQX                                  |                                                     |

| 3.   | •                               |                                              | a. Assert BDIN                                      |

|      |                                 |                                              | b. Assert IAKI                                      |

| 4.   |                                 | Assert BGX                                   |                                                     |

| 5.   | a. Assert SACK                  |                                              |                                                     |

|      | b. Negate BRX                   |                                              |                                                     |

| 6.   |                                 | a. Negate BBSY                               |                                                     |

|      |                                 | b. Negate IRQX                               |                                                     |

| 7.   |                                 | Negate BGX                                   |                                                     |

| 8.   | a. Assert BBSY                  |                                              |                                                     |

|      | b. Negate SACK                  |                                              |                                                     |

|      | c. Assert INTR                  |                                              |                                                     |

|      | d. Place vector on<br>DXX lines |                                              |                                                     |

| 9.   |                                 | Gate Interrupt vector from DXX to BDAL lines |                                                     |

| 10.  |                                 | Assert BRPLY                                 |                                                     |

| 11.  |                                 |                                              | a. Input vector on<br>BDAL lines and<br>negate BDIN |

|      |                                 |                                              | b. Remove IAKI                                      |

| 12.  |                                 | Assert SSYN                                  |                                                     |

| 13.  | a. Negate INTR                  |                                              |                                                     |

|      | b. Negate BBSY                  |                                              |                                                     |

| 14.  |                                 | a. Negate BRPLY                              |                                                     |

|      |                                 | b. Remove Interrupt vector from BDAL lines.  |                                                     |

|      |                                 | c. Remove SSYN                               |                                                     |

|      | SEQUENCE COMPLETED              |                                              |                                                     |

Table 7-7: UNIBUS Interrupt Sequence-Q BUS Arbitrator

Although most of the device response signals are ignored by the Q bus arbitrator, the signals are used by the QNIVERTER to properly time acknowledge (IAKI) and reply (RPLY) signals so that the requesting device can remove its signals in the proper sequence to insure a valid transfer.

### 7.1.4 INFORMATION TRANSFER AND DIRECT TO MEMORY CONTROL

As listed in Table 7-1 the logic blocks that make up the QNIVERTER information transfer and direct to memory (DMA) control are as follows:

- Transfer Control Transceivers

- CO, Cl, and NPG Logic

- Bus DMA Logic

- Direct Memory Control Transceivers

- O Bus Transfer Control Transceivers

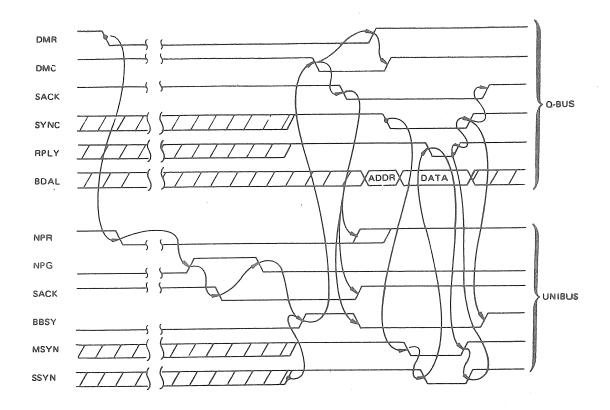

Three of the logic elements are primarily concerned with buffering the write/read transfer control (handshaking) signals between the two buses and buffering the four DMA control signals to the Q bus. The remaining two logic elements primarily match the characteristics of the Q bus DMA timing signal sequence with the Unibus NPR timing signal sequence. In Unibus terminology direct to memory requests are referred to as non-processor requests (NPR). Regardless of the terminology (NPR,DMA) the effect is the same in both systems; requests are made for data transfers directly to memory without processor intervention.

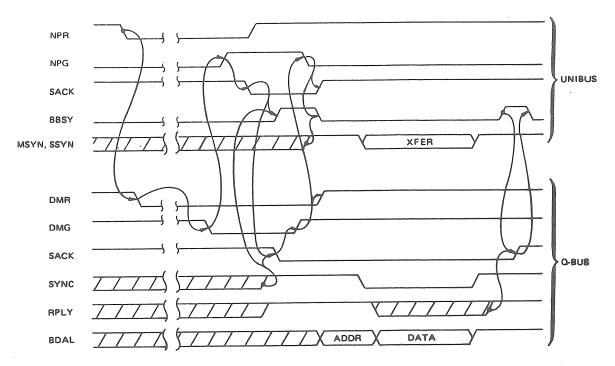

Figure and Table 7-8 illustrate the signal sequence for a DMA request when the Unibus is arbitrator. Figure and Table 7-9 illustrate the signal sequence for a DMA request when the Q bus is arbitrator. Note the similarity in the signal names and signal responses between the two buses. The major difference between the two buses is that transferring addresses and data to the Unibus is a one-step process and transferring addresses and data to the Q bus is a two-step process (address and data lines are time shared on the Q bus).

Mode control lines on the two buses have different terminology. In the Unibus system the device must decode the condition of control lines CO and Cl to determine if the required transfer sequence is a data in (DATI), a data in pause (DATIP), a data out (DATO), or a data out byte (DATOB). In Q bus devices detecting the required type of transfer is simpler. Q bus signal BDOUT specifies an output transfer, BDIN specifies either an input transfer or that an interrupt operation is occurring, and BWTBT specifies read/write operation and if the output transfer is on a byte basis. The CO, Cl portion of the CO, Cl, and NPG logic decodes and codes the mode control signals between the two buses.

Figure 7-8: DMA Request - Unibus Arkitrator

Figure 7-9: DMA Request - Q Bus Arbitrator

| STEP | Q BUS                                      | QNIVERTER                                                                      | UNIBUS       |

|------|--------------------------------------------|--------------------------------------------------------------------------------|--------------|

| 1.   | DMR Asserted                               |                                                                                |              |

| 2.   |                                            | NPR Asserted                                                                   |              |

| 3.   |                                            |                                                                                | NPG Asserted |

| 4.   |                                            | SACK Asserted                                                                  |              |

| 5.   |                                            |                                                                                | NPG Negated  |

| 6.   |                                            |                                                                                | BBSY Negated |

| 7.   |                                            | DMG Asserted                                                                   |              |

| 8.   | SACK Asserted                              | a. SACK negated                                                                |              |

|      |                                            | b. BBSY asserted                                                               |              |

| 9.   | DMR Negated                                |                                                                                |              |

| 10.  |                                            | DMG Negated                                                                    |              |

| 11.  | Place address on<br>BDAL lines             |                                                                                |              |

| 12.  |                                            | NPR Negated                                                                    |              |

| 13.  | a. Assert SYNC<br>b. Assert DOUT<br>or DIN |                                                                                |              |

| 14.  |                                            | <ul><li>a. Place address on</li><li>AXX lines</li><li>b. Assert MSYN</li></ul> |              |

| 15.  |                                            |                                                                                | Assert SSYN  |

| 16.  | Remove DOUT/DIN                            |                                                                                |              |

| 17.  |                                            | Negate MSYN                                                                    |              |

| 18.  |                                            |                                                                                | Remove SSYN  |

| 19.  | Remove SYNC                                |                                                                                |              |

| 20.  | Remove SACK                                |                                                                                |              |

| 21.  |                                            | Remove BBSY                                                                    |              |

| 22.  |                                            |                                                                                | Assert BBSY  |

|      | TRANSFER SEQUENCE (                        | COMPLETE                                                                       |              |

Table 7-8: Q Bus DMA Request - Unibus Arbitrator

| STEP | UNIBUS                                                                                                      | QNIVERTER                                                               | Q BUS                                   |

|------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------|

| 1.   | Assert NPR                                                                                                  |                                                                         |                                         |

| 2.   |                                                                                                             | Assert DMR                                                              | · ·                                     |

| 3.   |                                                                                                             |                                                                         | Assert DMG                              |

| 4.   |                                                                                                             | Assert NPG                                                              |                                         |

| 5.   | Assert SACK<br>(Unibus)                                                                                     |                                                                         |                                         |

| 6.   | Negate NPR                                                                                                  |                                                                         |                                         |

| 7.   |                                                                                                             |                                                                         | Negate SYNC (End of previous bus cycle) |

| 8.   |                                                                                                             | Assert SACK (Q Bus)                                                     |                                         |

| 9.   |                                                                                                             | Negate BBSY                                                             |                                         |

| 10.  |                                                                                                             |                                                                         | Negate DMG                              |

| 11.  |                                                                                                             | Negate NPG                                                              |                                         |

| 12.  | a. Negate SACK                                                                                              | a. Place address onto                                                   |                                         |

|      | (Unibus) b. Negate DMR c. Assert BBSY d. Place address on AXX lines e. Place data on DXX if write operation |                                                                         |                                         |

| 13.  | Assert MSYN                                                                                                 |                                                                         | ·                                       |

| 14.  |                                                                                                             | a. Switch Data to BDAL<br>lines from DXX lines<br>b. Assert DIN or DOUT |                                         |

| 15.  |                                                                                                             |                                                                         | Assert RPLY                             |

| 16.  |                                                                                                             | Assert SSYN                                                             |                                         |

| 17.  | Negate MSYN                                                                                                 |                                                                         |                                         |

| 18.  |                                                                                                             | Negate DIN or DOUT                                                      |                                         |

| 19.  |                                                                                                             | Remove RPLY                                                             |                                         |

| 20.  |                                                                                                             | Remove SSYN                                                             |                                         |

| 21.  |                                                                                                             | Remove SYNC                                                             |                                         |

| 22.  | Remove BBSY                                                                                                 |                                                                         |                                         |

| 23.  |                                                                                                             | Remove SACK                                                             |                                         |

|      | TRANSFER SEQUENC                                                                                            | E COMPLETED                                                             |                                         |

Table 7-9: Unibus DMA Request - Q Bus Arbitrator

### 7.2 UNIBUS I/O SIGNALS

| Signal Name | Description                                                                                                                                                                                                                                                                             |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A17 - A00   | Address bits. These bits select the slave device and/or memory address.                                                                                                                                                                                                                 |  |

| D15 - D00   | Data bits. These bits contain the information to be transferred.                                                                                                                                                                                                                        |  |

| CO, Cl      | Control lines. These lines specify the type of data transfer: DATI, DATIP, DATO, or DATOB.                                                                                                                                                                                              |  |

| MSYN        | Master sync. This signal is generated by the bus master to request a data transfer.                                                                                                                                                                                                     |  |

| SSYN        | Slave sync. This signal is generated by the slave device in response to MSYN to indicate that the device is ready with data for the bus or has read data from the bus. It is also generated by the processor during an interrupt to indicate that it has accepted the interrupt vector. |  |

| INTR        | Interrupt. This signal is generated by QNIVERTER along with the interrupt vector during an Interrupt sequence.                                                                                                                                                                          |  |

| BR4 - BR 7  | Bus request. One of these signals is used to request use of the bus for an interrupt at the level specified.                                                                                                                                                                            |  |

| BG4 - BG7   | Bus grant. This signal is generated by the processor to grant use of the bus for an interrupt at the specified level.                                                                                                                                                                   |  |

| NPR         | Non-processor request. This signal is generated by a DMA device to request use of the bus for a data transfer.                                                                                                                                                                          |  |

| BBSY        | Bus busy. This signal indicates that the Unibus is in use.                                                                                                                                                                                                                              |  |

| SACK        | Selection acknowledge. This signal is generated in response to Bus Grant to inhibit further bus grants and to indicate that a device is selected to use the bus upon completion of the sequence currently in progress.                                                                  |  |

### 7.3 Q BUS I/O SIGNALS

| Signal Name    | Description                                                                                                                                                                                                                                                                               |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAD16, BAD17   | Extended address bits.                                                                                                                                                                                                                                                                    |

| BBS7           | Bank 7 select. The bus master asserts BBS7 when an address in the upper 4K bank (I/O address) is placed on the bus.                                                                                                                                                                       |

| BDALO - BDAL15 | 16-line data/address bus over which address and data information are communicated. Address information is first placed on the bus by the bus master. The same device then either receives input data or supplies output data to the addressed slave device or memory over the same lines. |

| BDCOK          | DC power OK.                                                                                                                                                                                                                                                                              |

| BDIN           | Data input: specifies either an input operation or an interrupt operation.                                                                                                                                                                                                                |

| BDOUT          | Data output: specifies an output operation with respect to the bus master is taking place and data is stable on the data/address lines.                                                                                                                                                   |

| BDMG1, BDMG0   | DMA grant input and DMA grant output. Processor generated daisy-chained bus mastership grant signal to the highest priority DMA requesting device on the bus.                                                                                                                             |

| BEVNT          | External Event interrupt request.                                                                                                                                                                                                                                                         |

| BDMRL          | Direct memory access (DMA) request: requested by devices to gain bus mastership.                                                                                                                                                                                                          |

| BIAKI, BIAKO   | Interrupt Acknowledge input and interrupt acknow-ledge output. A daisy-chained signal generated by the processor in response to an interrupt request.                                                                                                                                     |

| BIRQ           | Interrupt request. asserted by a device to request service by the processor.                                                                                                                                                                                                              |

| BSACK          | Select acknowledge: asserted by a DMA in response to the BDMGO signal from the processor, indicating that the DMA device is bus master.                                                                                                                                                   |

| BRPLY          | Reply: asserted in response to BDIN or BDOUT and during IAK transactions by a slave device. Indicates either that the slave has placed data on the bus or has received data from the bus.                                                                                                 |